# OMAP35xx Applications Processor Introduction

## Texas Instruments OMAP<sup>™</sup> Family of Products

# **Technical Reference Manual**

Literature Number: SPRUFF1 February 2008

### WARNING: EXPORT NOTICE

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorisation from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

US ECCN: 3E991

EU ECCN: 3E991

And may require export or re-export license for shipping it in compliance with the applicable regulations of certain countries.

## Contents

| 1 | Intro | roduction |                                                                  |     |  |  |

|---|-------|-----------|------------------------------------------------------------------|-----|--|--|

|   | 1.1   | Overvi    | ew                                                               | . 6 |  |  |

|   | 1.2   | Enviro    | nment                                                            | . 8 |  |  |

|   | 1.3   | Descri    | ption                                                            | . 9 |  |  |

|   |       | 1.3.1     | MPU Subsystem                                                    | . 9 |  |  |

|   |       | 1.3.2     | IVA2.2 Subsystem                                                 | 10  |  |  |

|   |       | 1.3.3     | On-Chip Memory                                                   | 11  |  |  |

|   |       | 1.3.4     | External Memory Interfaces                                       | 11  |  |  |

|   |       | 1.3.5     | DMA Controllers                                                  | 12  |  |  |

|   |       | 1.3.6     | Multimedia Accelerators                                          | 12  |  |  |

|   |       | 1.3.7     | Security (HS Devices Only)                                       | 13  |  |  |

|   |       | 1.3.8     | Comprehensive Power Management                                   | 13  |  |  |

|   |       | 1.3.9     | Peripherals                                                      | 13  |  |  |

|   | 1.4   | Packa     | ge-On-Package Concept                                            |     |  |  |

|   | 1.5   | OMAP      | 35xx Family                                                      | 17  |  |  |

|   |       | 1.5.1     | Device Features                                                  | 17  |  |  |

|   |       | 1.5.2     | Device Identification                                            | 19  |  |  |

|   |       | 1.5.3     | General Recommendations Relative to Unavailable Features/Modules | 20  |  |  |

|   |       |           |                                                                  |     |  |  |

### List of Figures

| 1-1 | OMAP35xx Environment Using TWL4030                     | 8  |

|-----|--------------------------------------------------------|----|

| 1-2 | Block Diagram                                          | 9  |

| 1-3 | POP Concept (CBB Package)                              | 15 |

| 1-4 | Stacked Memory Package on the POP Device (CBB Package) | 15 |

| 1-5 | Stacked Memory Package on the POP Device (CBB Package) | 16 |

### List of Tables

| 1-1 | OMAP35xx Peripherals                                                              | 14 |

|-----|-----------------------------------------------------------------------------------|----|

| 1-2 | Summary of Memories Supported by the POP Interface                                | 16 |

| 1-3 | Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CBB Package) | 17 |

| 1-4 | Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CUS Package) | 18 |

| 1-5 | Device Identification Registers                                                   | 19 |

| 1-6 | CONTROL_IDCODE Register Definition                                                | 19 |

| 1-7 | Hawkeye Number Value                                                              | 20 |

| 1-8 | Revision Number Value                                                             | 20 |

| 1-9 | CONTROL_DIE_ID                                                                    | 20 |

This chapter introduces the features, supporting subsystems, and architecture of the OMAP35xx high-performance applications processors.

| Торіс |                            | Page |

|-------|----------------------------|------|

| 1.1   | Overview                   | 6    |

| 1.2   | Environment                | 8    |

| 1.3   | Description                | 9    |

| 1.4   | Package-On-Package Concept | 15   |

| 1.5   | OMAP35xx Family            | 17   |

#### 1.1 Overview

The OMAP35xx family of high-performance, applications processors are based on the enhanced OMAP<sup>™</sup> 3 architecture and are integrated on TI's advanced 65-nm process technology.

**Note:** The OMAP 3 architecture is configured with different sets of features in different devices. This technical reference manual details all of the features available in current and future OMAP35xx devices. Some features may not be available or supported in your particular device. For more information, see Section 1.5, *OMAP35xx Family* and your device-specific data manual.

The architecture is designed to provide best-in-class video, image, and graphics processing sufficient to support the following:

- Streaming video

- 2D/3D mobile gaming

- Video conferencing

- High-resolution still image

- Video capture in 2.5G wireless terminals, 3G wireless terminals, and rich multimedia-featured handsets, and high-performance personal digital assistants (PDAs).

This OMAP device also features the M-Shield<sup>™</sup> mobile security technology to enable more secure e-commerce applications and the replay of copyright-protected digital media content.

Security features integrated on the devices support applications designed for:

- Protection against malicious attacks

- M-commerce

- Content protection for recordable media (CPRM)

- Digital rights management (DRM)

High-security (HS) devices rely on a security scheme based on hardware mechanisms and a secure read-only memory (ROM) code, ensuring that only trusted code can access the secure resources. These resources are in specific regions of memories as well as in peripherals, hardware cryptographic accelerators, and eFuse keys. General-purpose (GP) devices do not include a security feature.

**Note:** This technical reference manual focuses only on general-purpose (GP) devices. To determine if a high-security (HS) version of your device is available and for more information on HS devices, see Section 1.5, *OMAP35xx Family*, and your device-specific data manual.

The device supports high-level operating systems (OSs), such as:

- Windows CE

- Symbian OS

- Linux

- Palm OS

This OMAP device includes state-of-the-art power-management techniques required for high-performance mobile products.

The following subsystems are part of the device:

- Microprocessor unit (MPU) subsystem based on the ARM Cortex-A8<sup>™</sup> microprocessor

- IVA2.2 subsystem with a C64x+ digital signal processor (DSP) core

- SGX530 subsystem for 2D and 3D graphics acceleration to support display and gaming effects

- **Note:** IVA2.2 and SGX are not available on all devices. See Section 1.5, *OMAP35xx Family*, for more information on available features.

- Camera image signal processor (ISP) that supports multiple formats and interfacing options connected to a wide variety of image sensors

- Display subsystem with a wide variety of features for multiple concurrent image manipulation, and a

programmable interface supporting a wide variety of displays. The display subsystem also supports

NTSC/PAL video out.

- Level 3 (L3) and level 4 (L4) interconnects that provide high-bandwidth data transfers for multiple initiators to the internal and external memory controllers and to on-chip peripherals

The device also offers:

- A comprehensive power and clock-management scheme that enables high-performance, low-power operation, and ultralow-power standby features. The device also supports SmartReflex<sup>™</sup> adaptative voltage control. This power management technique for automatic control of the operating voltage of a module reduces the active power consumption.

- A memory stacking feature using the package-on-package (POP) implementation (see Section 1.4, *Package-on-Package Concept*)

7

#### 1.2 Environment

This section provides an overview of the OMAP environment. The device is associated with a power integrated circuit (IC). Texas Instruments provides a global solution with the TWL4030 device. For more information on the TWL4030 device, contact your TI representative.

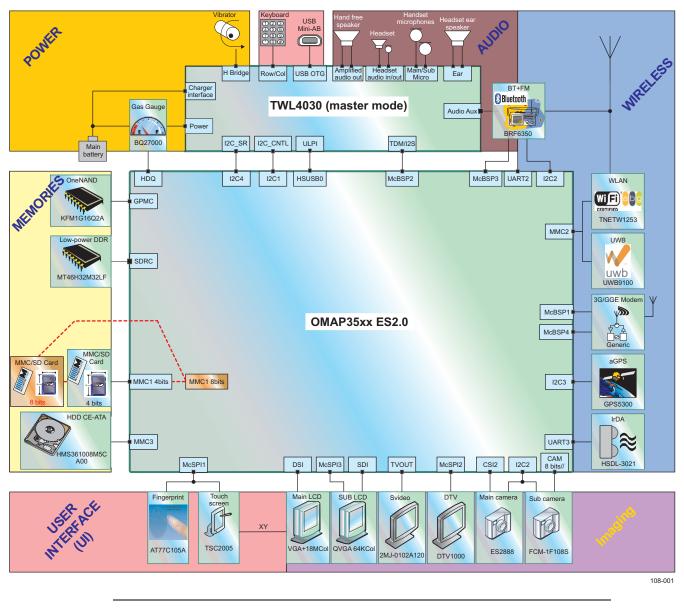

Figure 1-1 provides an overview of a nonexhaustive environment for the high-tier OMAP35xx device.

Figure 1-1. OMAP35xx Environment Using TWL4030

**Note:** Some features are not available on all devices. See Section 1.5, *OMAP35xx Family*, for more information on available features.

#### 1.3 Description

The device is offered in two packages:

- CBB package: 515-ball, 12 x 12 mm, package-on-package (POP) 0.5-mm (top) and 0.4-mm (bottom) ball pitch package. Some balls are available at the top of the device to allow memory stacking. For more information, see Section 1.4, *Package-on-Package Concept*.

- CUS package: 423-ball, 16 x 16mm, 0.65-mm (bottom) ball pitch package

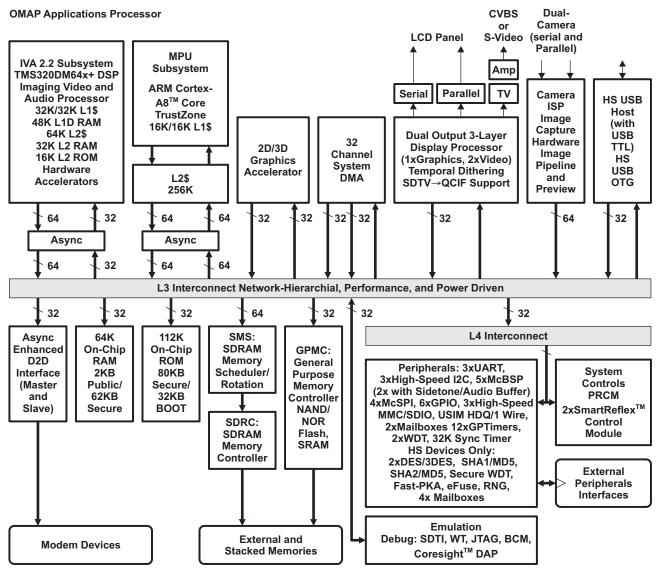

Figure 1-2 shows the block diagram.

**Note:** Some features are not available on all devices. See Section 1.5, *OMAP35xx Family*, for more information on available features.

#### 1.3.1 MPU Subsystem

The MPU subsystem integrates the following modules

• ARM subchip

- ARM Cortex-A8 core

- ARM Version 7<sup>™</sup> ISA: Standard ARM instruction set + Thumb®-2, Jazelle® RCT Java accelerator, and media extensions

- NEON<sup>™</sup> SIMD coprocessor (VFP lite + media streaming instructions)

- Cache memories

- Level 1: 16KB instruction and 16KB data—4-way set associative cache, 64 bytes/line

- Level 2: see Section 1.5, OMAP35xx Family.

- Interrupt controller (MPU IN TC) of 96 synchronous interrupt lines

- Asynchronous interface with core logic

- Debug, trace, and emulation features: ICE-Crusher, ETM, ETB modules.

#### 1.3.2 IVA2.2 Subsystem

The device includes a high-performance imaging video and audio (IVA2.2) accelerator based on the Texas Instruments TMS320DMC64x+ VLIW DSP core.

The IVA2.2 subsystem includes the following main features:

- 32-bit fixed-point media processor

- Very long instruction word (VLIW) architecture based on the programmable enhanced version of C64x DSP core

- Eight instructions/cycle, eight execution units

- Optimized instruction set for video and imaging processing

- Eight 8 x 8 or 16 x 16 multiply accumulate (MAC) per cycle

- Eight slave asynchronous die (SAD) per cycle

- Eight interpolations (a + b + 1)>>1 per cycle

- Two (32-bit x 32-bit > 64-bit) multiply operations per cycle

- Low-power processor and megacell

- Dynamically mixed 32-bit and 16-bit instruction sets

- Software pipelined loop (SPLOOP) instruction buffer

- Separate power domain

- Supported multiple power-down states

- Two-level memory subsystem hierarchy

- L1P (program)

- 32KB direct-mapped cache—32-byte cache line, configurable as cache or memory mapped (Possible values are: 0KB cache/32KB memory, 4KB/28KB, 8KB/24KB, 16KB/16KB, or 32KB/0KB)

- L1D (data)

- 32KB 2-way set associative cache—4-byte cache line, configurable as cache or memory mapped (Possible values are: 0KB cache/32KB memory, 4KB/28KB, 8KB/24KB, 16KB/16KB, or 32KB/0KB)

- 48KB memory-mapped SRAM

- L2 (program and data)

- 64KB 4-way set associative cache—128-byte cache line, configurable as cache or memory mapped (Possible values are: 0KB cache/64KB memory, 32KB/32KB, or 64KB/0KB)

- 32KB memory-mapped SRAM

- 16KB ROM

- Video hardware accelerators

- Improved motion estimation (iME) dedicated hardware

- Improved loop filtering (iLF) dedicated hardware

- Improved variable length coder/decoder (iVLCD) with quantizing capabilities dedicated hardware

- Video dedicated sequencer

- Video local interconnect

- Local level 2 (L2) memory interface/arbiter

- Private direct memory access (DMA) controller:

- 128 logical channels

- 1D/2D addressing

- Chaining capability

- Fully pipelined, two 64-bit read ports, two 64-bit write ports

- Single access 32-byte or 64-byte incrementing bursts

- Level 1 (L1) interrupt controller (INTC)

- Local IVA2.2 digital phase-locked loop (DPLL) supplying the IVA2.2 subsystem clocking

- 32-entry memory management unit (MMU) for seamless integration in high-level OS environment

- IVA2.2 system interfaces

- 64-bit L3 port shared for external memory accesses

- Multithreaded link shared by DSP core and DMA accesses

- Interface with the L3 interconnect that can be synchronous or asynchronous for clock decoupling between IVA2.2 and L3 interconnect

- Incrementing burst support

- Critical line first to reduce line fetch latency to the processor

- Host port interface (HPI) for MMU programming and access to the IVA2.2 internal memories. Can be synchronous or asynchronous

- System interfaces: clocking, power management

- C-friendly environment (state-of-the-art C compiler for VLIW architecture)

- Texas Instruments low-overhead DSP-BIOS operating system

**Note:** IVA2.2 is not available on all devices. See Section 1.5, *OMAP35xx Family*, for more information on available features.

#### 1.3.3 On-Chip Memory

On-chip memory configuration offers memory resources for program and data storage:

- 112KB ROM

- 64KB single-access static random access memory (SRAM)

#### 1.3.4 External Memory Interfaces

The device includes two external memory interfaces supporting the stacking of a multichip memory package using the generic POP interface:

- General-purpose memory controller (GPMC)

- NOR flash, NAND flash (with ECC Hamming code calculation), SRAM and Pseudo-SRAM asynchronous and synchronous protocols

- Flexible asynchronous protocol control for external ASIC or peripheral interfacing

- 16-bit data, up to 8 chip-selects (CSs)

- 128M-byte addressable per chip-select, 1G-byte total address space

- Nonmultiplexed device with limited address (2K bytes)

- SDRAM controller (SDRC)

- Mobile single data rate (M-SDR) SDRAM and low-power double data rate (LPDDR) SDRAM

- 16-bit or 32-bit data, 2 chip-selects, configurations for a maximum of 1 G-byte address space per chip-select

- Work in conjunction with the SDRAM memory scheduler (SMS) companion module

#### 1.3.5 DMA Controllers

The device embeds one generic DMA controller, the system DMA (sDMA) controller, used for memory-to-memory, memory-to-peripheral, and peripheral-to-memory transfers:

- One read port, one write port

- 32 prioritizable logical channels

- 96 hardware requests

- 256 x 32-bit FIFO dynamically allocable between active channels

The device also embeds three dedicated DMA controllers: enhanced DMA (EDMA), which is embedded in the IVA2.2 subsystem, display DMA, and USB HS DMA.

#### 1.3.6 Multimedia Accelerators

The device uses the following multimedia accelerators for display and gaming effects as well as high-end imaging and video applications:

- 2D and 3D graphics accelerator (SGX or SGX530)

- 2D and 3D graphics and video codecs supported on common hardware

- Tile-based architecture

- Universal scalable shader engine (USSE<sup>™</sup>) multithreaded engine incorporating pixel and vertex shader functionality reducing die area

- Advanced shader feature set in excess of Microsoft VS3.0, PS3.0, and OGL2.0

- Industry standard API support Direct3D mobile, OGL-ES 1.1 and 2.0, OpenVG 1.0, OpenMax

- Fine-grained task switching, load balancing, and power management

- Programmable high-quality image anti-aliasing

- Advanced geometry DMA driven operation for minimum CPU interaction

- Fully virtualized memory addressing for OS operation in a unified memory architecture

- Advanced and standard 2D operations (that is, vector graphics, BLTs, ROPs, etc.)

- Programmable video encode and decode support for H.264, H.263, MPEG4 (SP), WMV9, and JPEG

**Note:** Multimedia accelerators are not available on all devices. See Section 1.5, OMAP35xx *Family*, for more information on available features.

- Camera interface

- Supports most of the raw image sensors available in the market

- Serial interface compatible with the CCP2/MIPI CSI1 specification (CSIb) and the MIPI CSI2 specification (CSIa)

- Includes video processing hardware

- 12-bit parallel interface supported

- Pixel clock up to 83 MHz

#### CAUTION

Clock configurations depend on the core voltage and maximum clock frequencies. Values in this document might not apply to production devices. Refer to your device-specific data manual for supported values for production devices.

- Embedded DMA controller in CSI2 receiver

- Display interface

- Display controller

- Color and monochrome displays up to 2048 x 2048 x 24-bpp resolution

- 256 x 24-bit entries palette in red, green, blue (RGB)

- 3,375 colors, 15 grayscales

- Picture-in-picture (overlay), color-space conversion, rotation, color-phase rotation, and resizing support

- Remote frame buffer interface

- Liquid-crystal display (LCD) pixel interfaces (MIPI DPI 1.0) and LCD bus interfaces (MIPI DBI 1.0) supported

- NTSC/PAL video encoder outputs with integrated digital-to-analog converters (DACs) output are supported on CVBS and S-video TV analog output signals

- Serial display interface implements high-speed differential output buffers to support FlatLink3G<sup>™</sup>, Mobile CMADS and MIPI DSI 1.0 formats

- Embedded DMA controller

#### 1.3.7 Security (HS Devices Only)

The secure firmware resides in a secure version of the ROM and includes hardware security features that enable HS devices and the following encryption/decryption accelerators:

- RNG

- 2 x DES/3DES

- SHA1/MD5

- SHA2/MD5

- 2 x AES with counter mode

- Fast PKA

The customer programmable fuse ROM (CPFROM) module is only available on high-security (HS) devices.

The universal subscriber identity module (USIM) that supports 3GPP extended features and EMV specific feature is available only on HS devices. This interface includes two modules: the fast-deactivate (FD) module and the USIM.

**Note:** This technical reference manual focuses only on general-purpose (GP) devices. To determine if a high-security (HS) version of your device is available and for more information on HS devices, see Section 1.5, *OMAP35xx Family*, and your device-specific data manual.

#### 1.3.8 Comprehensive Power Management

OMAP35xx devices include the following power management features:

- Clock and reset generation and distribution

- Wake-up event management

- SmartReflex<sup>™</sup> technology

- Dynamic voltage frequency shifting

- Dynamic power shifting

- Static leakage management

#### 1.3.9 Peripherals

The device supports a comprehensive set of peripherals to provide flexible and high-speed interfacing and on-chip programming resources. Table 1-1 provides a list and description of the peripherals available on OMAP35xx devices.

| Туре                                                | Name                                                                                 | Number               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                     | Multi-channel Buffered<br>Serial Ports (McBSPs)                                      | 5                    | The McBSPs provide a full-duplex direct serial interface between<br>the device and other devices in a system such as audio and<br>voice codecs and other application chips.<br>McBSP1, McBSP2, and McBSP3 serve as general purpose<br>serial ports while McBSP2 and McBSP3 include additional<br>audio-loopback capability.                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                     | Multi-channel Serial Port<br>Interface (McSPI)                                       | 4                    | The McSPIs provide a master/slave interface to SPI devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Serial Communication                                | High-speed Multi-port<br>USB Host Controller                                         | 1                    | High-speed USB2.0 host controller with three host ports each offering high-speed data transactions (up to 480 Mbps) or full-speed/low-speed data transactions (12 and 1.5 Mbps, respectively). In high-speed mode, the USB host controller ports interface to external USB PHYs using a 12-pin or 8-pin UTMI low pin interface (ULPI). In full-speed and low-speed mode, the ports interface to external USB PHYs using a 6-/4-/3-pin serial interface. Additionally each port can be directly connected to a USB device (bypassing the need for USB PHY) by using an the on-chip transceiver-less link logic (TLL) adapter. |  |  |  |

|                                                     | High-speed USB OTG<br>Controller                                                     | 1                    | High-speed USB2.0 OTG controller that offers high-speed data<br>transactions (up to 480 Mbps) on a USB port with embedded<br>DMA controller.<br>The high-speed USB OTG controller interfaces to an external<br>USB PHY using a 12-pin UTMI low pin interface (ULPI).                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                     | HDQ/1-Wire                                                                           | 1                    | The HDQ/1-Wire interface supports the Benchmark HDQ protocol and the Dallas Semiconductor 1-Wire protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                     | Universal Asynchronous<br>Receiver/Transmitter<br>(UART)                             | 3                    | Serial communication interfaces compatible to the industry<br>standard TL16C550 asynchronous communications element.<br>UART1 and UART 2 are general serial communication<br>interfaces. UART3 provides additional support for infrared data<br>association (IrDA) and consumer infrared (CIR) communications.                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                     | High-speed (HS)<br>Inter-integrated Circuit<br>(I2C) Controllers                     | 3 <sup>(1)</sup>     | Master/slave I2C high-speed standard interfaces with support for standard mode (up to 100K bits/s), fast mode (up to 400K bits/s), and high-speed mode (up to 3.4M bits/s).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Removable Media                                     | Multimedia Card/Secure<br>Digital/Secure Digital I/O<br>(MMC/SDIO) Card<br>Interface | 1                    | MMC memory card, SD memory card, or SDIO cards interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                     | GP timers                                                                            | 12                   | Twelve general-purpose timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                     | Watchdog timers<br>(WDTs)                                                            | 2                    | Three watchdog timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                     | 32-kHz synchronization timer                                                         | 1                    | 32-kHz clock timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Miscellaneous                                       | General-purpose<br>input/output (GPIO)                                               | Package-<br>specific | General-purpose input/output pins controlled by six GPIO controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                     | Mailbox                                                                              | 6                    | MPU/IVA2.2 inter-processor communications mailboxes. All six mailboxes are available in chassis mode, however, only two mailboxes are available in stand-alone mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                     | Control module                                                                       | 1                    | I/O multiplexing and chip-configuration control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Security Modules<br>(High-security Devices<br>Only) |                                                                                      |                      | RNG, Fast PKA, 2xDES/3DES, SHA1/MD5, SHA2/MD5, 2xAES, Secure Watchdog Timer, and universal subscriber identity module (USIM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

Table 1-1. OMAP35xx Peripherals

<sup>(1)</sup> A fourth master/transmitter high-speed I2C interface (I2C4) is included in the power, reset, and clock management (PRCM) module to perform dynamic voltage control and power sequencing.

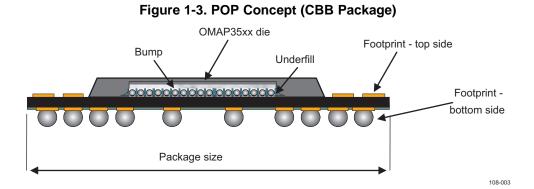

#### 1.4 Package-On-Package Concept

The OMAP35xx CBB package provides a package-on-package (POP) memory interface to support multiple stacked package configurations, including a flash multi-chip package, depending on customer needs. Note that use of standalone memory devices is also possible on the CBB package; use of POP technology is not required.

The stacked memory package is directly connected to the two memory interfaces (GPMC and SDRC) of the OMAP35xx CBB package through the POP interface present at the top. For more information on the interconnect between the stacked memory package and the OMAP35xx CBB package, see Chapter 11, Memory Subsystem, and your device-specific OMAP35xx data manual.

**Note:** Before using the POP memory interface, a compatible memory device supply must first be secured directly from specific memory vendors.

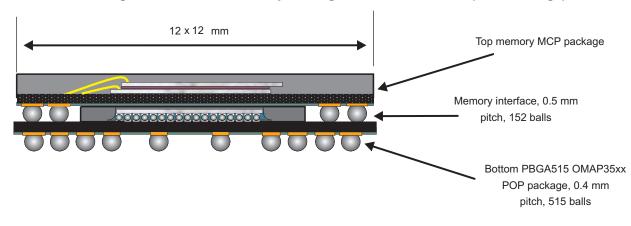

Figure 1-3 shows the concept of the POP solution, and Figure 1-4 shows stacked memory package on the POP device.

Figure 1-4. Stacked Memory Package on the POP Device (CBB Package)

108-004

The memory interfaces should be correctly configured based on the memory package used with the POP device.

Table 1-2 summarizes the supported configurations with the generic POP interface.

**Note:** Use of standalone memory devices is also possible on the CBB package; use of POP technology is not required.

| Generic POP Interface Features Set | SDRC Interface | GPMC Interface                                          |

|------------------------------------|----------------|---------------------------------------------------------|

| Type of memory supported           | MDDR           | NOR flash asynchronous and synchronous burst<br>flash   |

|                                    |                | NAND flash "CE don't care"                              |

|                                    |                | One NAND on CS0 and CS1                                 |

|                                    |                | NOR flash address/data nonmultiplexed is not supported. |

| Number of chip-selects             | 2              | 2                                                       |

| Maximum density per chip-select    | 1G bit         | 512M bits (NOR flash) or 4G bits NAND flash             |

| Maximum size per interface         | 2G bits        | 1G bit (NOR flash) or 8G bits NAND flash                |

| Interface width                    | X 32 bits      | X 16 bits                                               |

| I/O voltage                        | 1.8 V LVCMOS   | 1.8 V LVCMOS                                            |

For more information on the memory interface configuration, see the *Memory Subsystem* chapter.

The POP device includes feedthroughs in addition to the GPMC and SDRC interfaces positioned at the top of the package. Up to 47 feedthroughs are defined from the bottom ball-grid array (BGA) to the top (or POP) interface to support different memory combinations.

The feedthroughs either provide power to a top memory device or provide specific memory signals (for example, control and/or address signals) from the bottom BGA to the POP interface.

**Note:** It is possible to monitor the DDR SDRAM temperature if the memory multichip package allows the temperature sensing option. A feedthrough is used to lower the temperature sensing dedicated signal to make a connection with a GPIO. For more information on DDR SDRAM temperature sensing management, see the *Memory Subsystem* and the *General-Purpose Interface* chapters.

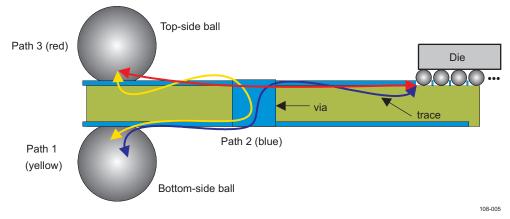

Figure 1-5 shows the implementation of feedthroughs on the POP and the different paths between the bottom and the top of the package.

#### Figure 1-5. Stacked Memory Package on the POP Device (CBB Package)

- (1) Path 1: feedthrough only; Path 2: all but feedthrough; Path 3: POP interface (SDRC + subset GPMC)

- (2) Any signal available on the POP interface to a top-side ball is also available to a bottom-side ball.

#### 1.5 OMAP35xx Family

The OMAP 3 architecture is configured with different sets of features in different devices. This technical reference manual details all of the features available in current and future OMAP35xx devices. Some features may not be available or supported in your particular device. The features supported across different OMAP35xx devices are shown on Table 1-3 (CBB package) and Table 1-4 (CUS package). For more information on the CBB and CUS package refer to your device-specific data manual.

| Раскаде)                                                  |         |          |          |          |          |  |  |

|-----------------------------------------------------------|---------|----------|----------|----------|----------|--|--|

| Subsystem/Co-Processor/Peripheral                         | Chapter | OMAP3530 | OMAP3525 | OMAP3515 | OMAP3503 |  |  |

| IVA2.2 Subsystem                                          | 14      | ü        | ü        |          |          |  |  |

| 2D/3D Graphics Accelerator                                | 13      | ü        |          | ü        |          |  |  |

| Cortex-A8 Neon Co-Processor                               | 3       | ü        | ü        | ü        | ü        |  |  |

| SDRAM Controller                                          | 11      | ü        | ü        | ü        | ü        |  |  |

| General-Purpose Memory Controller                         | 11      | ü        | ü        | ü        | ü        |  |  |

| Package-on-Package                                        | 1       | ü        | ü        | ü        | ü        |  |  |

| Chassis Mode                                              | 1       |          |          |          |          |  |  |

| Intersystem Communication<br>Registers (ICRs)             |         |          |          |          |          |  |  |

| Modem Interrupt Controller<br>Registers                   |         |          |          |          |          |  |  |

| Four Mailboxes                                            |         |          |          |          |          |  |  |

| Slave Die-to-Die (SAD2D)                                  |         |          |          |          |          |  |  |

| Module Master Die-to-Die<br>(MAD2D)                       |         |          |          |          |          |  |  |

| Module SMX Firewall for<br>Asynchronous Die-to-Die (AD2D) |         |          |          |          |          |  |  |

| Camera ISP                                                | 12      | ü        | ü        | ü        | ü        |  |  |

| Camera Serial Interface 1 (CSI1)                          |         |          |          |          |          |  |  |

| Camera Serial Interface 2 (CSI2)                          |         |          |          |          |          |  |  |

| Display Subsystem                                         | 15      | ü        | ü        | ü        | ü        |  |  |

| LCD and TV Output Interface                               |         | ü        | ü        | ü        | ü        |  |  |

| Serial Display Interface (SDI)                            |         |          |          |          |          |  |  |

| Display Serial Interface (DSI)                            |         |          |          |          |          |  |  |

| McBSP1/2/3/4/5                                            | 22      | ü        | ü        | ü        | ü        |  |  |

| McSPI1/2/3/4                                              | 20      | ü        | ü        | ü        | ü        |  |  |

| High-Speed USB OTG Controller                             | 25      | ü        | ü        | ü        | ü        |  |  |

| High-Speed USB Host Controller                            | 25      | ü        | ü        | ü        | ü        |  |  |

| HDQ/1-Wire                                                | 21      | ü        | ü        | ü        | ü        |  |  |

| UART1/2                                                   | 18      | ü        | ü        | ü        | ü        |  |  |

| UART3/IrDA/CIR                                            | 18      | ü        | ü        | ü        | ü        |  |  |

| I2C1/2/3                                                  | 19      | ü        | ü        | ü        | ü        |  |  |

| MMC/SD/SDIO1/2/3                                          | 23      | ü        | ü        | ü        | ü        |  |  |

| GP Timer (x12)                                            | 26      | ü        | ü        | ü        | ü        |  |  |

| Watchdog Timer (x2)                                       | 26      | ü        | ü        | ü        | ü        |  |  |

| 32-kHz Sync Timer                                         | 26      | ü        | ü        | ü        | ü        |  |  |

| GPIO                                                      | 26      | ü        | ü        | ü        | ü        |  |  |

Table 1-3. Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CBB Package)

#### Table 1-3. Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CBB Package) (continued)

| Subsystem/Co-Processor/Peripheral    | Chapter | OMAP3530 | OMAP3525 | OMAP3515 | OMAP3503 |

|--------------------------------------|---------|----------|----------|----------|----------|

| Secure ROM                           | 1       |          |          |          |          |

| RNG                                  | 1       |          |          |          |          |

| DES/3DES                             | 1       |          |          |          |          |

| SHA1/MD5                             | 1       |          |          |          |          |

| SHA2/MD5                             | 1       |          |          |          |          |

| AES                                  | 1       |          |          |          |          |

| Fast PKA                             | 1       |          |          |          |          |

| Secure Watchdog Timer                | 1       |          |          |          |          |

| Universal Subscriber Identify Module | 1       |          |          |          |          |

| High-security Device                 | 1       |          |          |          |          |

| General-purpose Device               | 1       | ü        | ü        | ü        | ü        |

#### Table 1-4. Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CUS Package) .

|                                            |                 | rackayej |          |          |          |          |

|--------------------------------------------|-----------------|----------|----------|----------|----------|----------|

| Subsystem/Co-Processor/                    | Peripheral      | Chapter  | OMAP3530 | OMAP3525 | OMAP3515 | OMAP3503 |

| IVA2.2 Subsystem                           |                 | 14       | ü        | ü        |          |          |

| 2D/3D Graphics Accelerator                 |                 | 13       | ü        |          | ü        |          |

| Cortex-A8 Neon Co-Processor                |                 | 3        | ü        | ü        | ü        | ü        |

| SDRAM Controller                           |                 | 11       | ü        | ü        | ü        | ü        |

| General-Purpose Memory Controller          | (1)             | 11       | ü        | ü        | ü        | ü        |

| Package-on-Package                         |                 | 1        |          |          |          |          |

| Chassis Mode                               |                 | 1        |          |          |          |          |

| Intersystem Communic<br>(ICRs)             | ation Registers |          |          |          |          |          |

| Modem Interrupt Contr                      | oller Registers |          |          |          |          |          |

| Four Mailboxes                             |                 |          |          |          |          |          |

| Slave Die-to-Die (SAD                      | 2D)             |          |          |          |          |          |

| Module Master Die-to-                      | Die (MAD2D)     |          |          |          |          |          |

| Module SMX Firewall f<br>Die-to-Die (AD2D) | or Asynchronous |          |          |          |          |          |

| Camera ISP                                 |                 | 12       | ü        | ü        | ü        | ü        |

| Camera Serial Interfac                     | e 1 (CSI1)      |          |          |          |          |          |

| Camera Serial Interfac                     | e 2 (CSI2)      |          |          |          |          |          |

| Display Subsystem                          |                 | 15       | ü        | ü        | ü        | ü        |

| LCD and TV Output In                       | terface         |          | ü        | ü        | ü        | ü        |

| Serial Display Interface                   | e (SDI)         |          |          |          |          |          |

| Display Serial Interface                   | e (DSI)         |          |          |          |          |          |

| McBSP1/2/3/4/5                             |                 | 22       | ü        | ü        | ü        | ü        |

| McSPI1/2/3/4 <sup>(2)</sup>                |                 | 20       | ü        | ü        | ü        | ü        |

| High-Speed USB OTG Controller              |                 | 25       | ü        | ü        | ü        | ü        |

| High-Speed USB Host Controller (3)         |                 | 25       | ü        | ü        | ü        | ü        |

| HDQ/1-Wire                                 |                 | 21       | ü        | ü        | ü        | ü        |

(1) Chip select pins gpmc\_ncs1 and gpmc\_ncs2 as well as wait pins gpmc\_wait1 and gpmc\_wait2 are not available on the CUS package. (2)

Chip select pins mcspi1\_cs1 and mcspi\_cs2 are not available on the CUS package. High-speed USB host controller port 3 is not available on the CUS package.

(3)

| Subsystem/Co-Processor/Peripheral    | Chapter | OMAP3530 | OMAP3525 | OMAP3515 | OMAP3503 |

|--------------------------------------|---------|----------|----------|----------|----------|

| UART1/2 <sup>(4)</sup>               | 18      | ü        | ü        | ü        | ü        |

| UART3/IrDA/CIR                       | 18      | ü        | ü        | ü        | ü        |

| I2C1/2/3                             | 19      | ü        | ü        | ü        | ü        |

| MMC/SD/SDIO1/2/3                     | 23      | ü        | ü        | ü        | ü        |

| GP Timer (x12)                       | 26      | ü        | ü        | ü        | ü        |

| Watchdog Timer (x2)                  | 26      | ü        | ü        | ü        | ü        |

| 32-kHz Sync Timer                    | 26      | ü        | ü        | ü        | ü        |

| GPIO <sup>(4)</sup>                  | 26      | ü        | ü        | ü        | ü        |

| Secure ROM                           | 1       |          |          |          |          |

| RNG                                  | 1       |          |          |          |          |

| DES/3DES                             | 1       |          |          |          |          |

| SHA1/MD5                             | 1       |          |          |          |          |

| SHA2/MD5                             | 1       |          |          |          |          |

| AES                                  | 1       |          |          |          |          |

| Fast PKA                             | 1       |          |          |          |          |

| Secure Watchdog Timer                | 1       |          |          |          |          |

| Universal Subscriber Identify Module | 1       |          |          |          |          |

| High-security Device                 | 1       |          |          |          |          |

| General-purpose Device               | 1       | ü        | ü        | ü        | ü        |

# Table 1-4. Subsystem, Co-Processor, and Peripheral Support on OMAP35xx Devices (CUS Package) (continued)

(4) A maximum of 170 GPIO pins are supported. The following GPIO pins are not available: gpio\_52, gpio\_53, gpio\_63 gpio\_64, gpio\_144, gpio\_145, gpio\_146, gpio\_152, gpio\_152, gpio\_154, gpio\_155, gpio\_175, and gpio\_176. Pin muxing restricts the total number of GPIO pins available at one time. See your device-specific data manual for more information on pin multiplexing.

#### 1.5.2 Device Identification

The identification registers include the CONTROL\_IDCODE and CONTROL\_DIE\_ID data registers. These registers are accessible through the L4 interconnect port starting at physical address 0x4830 A204 and 0x4830 A218, respectively. See the Memory Mapping chapter for more information about the L4 memory space mapping. Table 1-5 and Table 1-9 describe the identification registers.

The silicon type can be read in the HAWKEYE bit field value of the CONTROL.CONTROL\_IDCODE register. The silicon revision can be read in the VERSION bit field value of the CONTROL.CONTROL\_IDCODE register.

| Table 1-5. Device Identification Registers    |             |      |  |  |  |  |

|-----------------------------------------------|-------------|------|--|--|--|--|

| Register Name                                 | Address     | Size |  |  |  |  |

| CONTROL.CONTROL_IDCODE[31:0]                  | 0x4830 A204 | 32   |  |  |  |  |

| CONTROL.CONTROL_DIE_ID[127:0] 0x4830 A218 128 |             |      |  |  |  |  |

| Table 1-6. CONTROL_IDCODE Register Definition |         |                |                 |

|-----------------------------------------------|---------|----------------|-----------------|

| Field                                         | Bits    | Value          | Comment         |

| CONTROL.CONTROL_IDCODE [31:28]                | VERSION | See Table 1-8. | Revision number |

| CONTROL.CONTROL_IDCODE<br>[27:12]             | HAWKEYE | See Table 1-7. | Hawkeye number  |

| Field                         | Bits   | Value | Comment                    |

|-------------------------------|--------|-------|----------------------------|

| CONTROL.CONTROL_IDCODE [11:1] | TI_IDM | 0x13  | Manufacturer identity (TI) |

| CONTROL.CONTROL_IDCODE [0]    |        | 0x1   | Always set to 1.           |

#### Table 1-6. CONTROL\_IDCODE Register Definition (continued)

The Hawkeye number is hardcoded in the design. Table 1-7 lists the Hawkeye number values, and Table 1-8 lists the revision number values.

| Table 1- | 7. Hawkeye | Number | Value |

|----------|------------|--------|-------|

|----------|------------|--------|-------|

| Silicon Type   | Field                         | Value  |

|----------------|-------------------------------|--------|

| OMAP35xx ES2.0 | CONTROL.CONTROL_IDCODE[27:12] | 0xB7AE |

| OMAP35xx ES2.1 | CONTROL.CONTROL_IDCODE[27:12] | 0xB7AE |

#### Table 1-8. Revision Number Value

| Silicon Type | Field                         | Value |

|--------------|-------------------------------|-------|

| ES 2.0       | CONTROL.CONTROL_IDCODE[31:28] | 0000  |

| ES 2.1       | CONTROL.CONTROL_IDCODE[31:28] | 0001  |

The CONTROL.CONTROL\_IDCODE value is 0x0B7A E02F for OMAP35xx ES2.0.

The CONTROL.CONTROL\_IDCODE value is 0x1B7A E02F for OMAP35xx ES2.1.

The CONTROL.CONTROL\_DIE\_ID register is the 128 bits single identifier of the device.

#### Table 1-9. CONTROL\_DIE\_ID

| Field         | Bits     | Value             |

|---------------|----------|-------------------|

| DIE_ID[127:0] | RESERVED | Single identifier |

#### 1.5.3 General Recommendations Relative to Unavailable Features/Modules

As explained in the previous section, some features are not available in all OMAP35xx devices. For unavailable features, use the following recommendations:

- Memory mapping: Memory area of unavailable modules and features are RESERVED, read is undefined, and write can lead to unpredictable behavior.

- Interrupt controllers: Ensure that interrupts of unavailable modules and features are masked in MPU/IVA subsystems.

- DMA: Ensure that DMA requests of unavailable modules and features are masked in DMA subsystems.

- System Control Module (SCM): Unavailable modules and feature pins are not functional and should not be used.

- Power, Reset, and Clock Management Module (PRCM): For power management and power-saving consideration, ensure that power domains of unavailable features/modules are switched off and clocks are cut off.

- Interconnect: To flag potential interconnect outstanding commands, the time-out of target agents attached to unavailable modules can be enabled with the lowest setting.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated